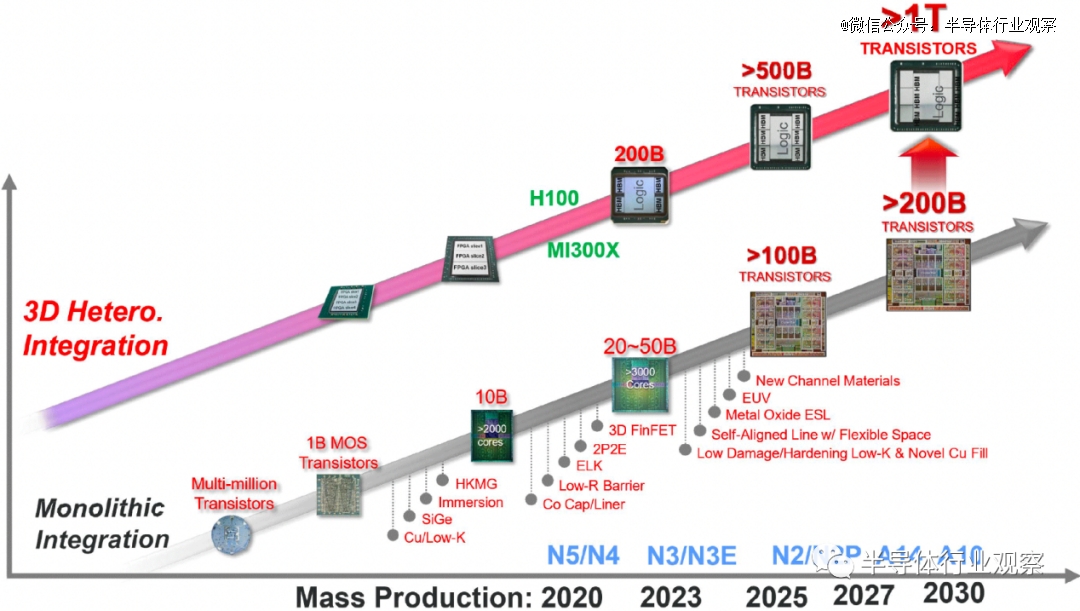

据tomshardware报道,在今年的IEDM 会议上,台积电突然分享了一个包含 1 万亿晶体管的芯片封装路线。据台积电所说,这些庞然大物将来自于单个芯片封装上的 3D 封装芯粒集合。与此同时,如图所示,台积电也在致力于开发在单片硅上包含 2000 亿个晶体管的芯片。

为了实现这一目标,该公司重申正在致力于 2 纳米级 N2 和 N2P 生产节点以及 1.4 纳米级 A14 和 1 纳米级 A10 制造工艺,这些工艺预计将于 2030 年完成。此外,台积电预计封装技术将将其取得进步,使其能够在 2030 年左右构建封装超过一万亿个晶体管的大规模多Chiplet解决方案。

而在这背后,则是芯片设计范式转变的无奈选择。

单片集成,强弩之末

自戈登摩尔定义“摩尔定律”以来,芯片产业一直在这个墨守成规的行业金科玉律指导下继续发展。在集成电路发明之后的几十年里,大多数芯片单位尺寸上集成的晶体管数量都呈现指数级增长,芯片的性能也同时水涨船高。

但是,进入到最近几年,受限于材料本身的物理特性,制造设备和工艺、架构的瓶颈。像过往那样在单芯片上集成更多的晶体管越来越难。但是,在人工智能和自动驾驶汽车需求的推动下,市场对芯片高性能有着极高的需求。这就使得持续增加芯片性能,成为了必然之路。过往一直使用的单片集成的方案还有着不小的吸引力,英伟达和Cerebras就是其中最忠诚的捍卫者。首先看英伟达,该公司推出的拥有 800 亿晶体管的GH100就是市场上最复杂的单片处理器之一。再看Cerebras,这家新创公司在一整块晶圆上实现了 2.5 万亿晶体管的集成。

之所以大家那么“念旧”,这与单片集成本身的特点有着莫大的关系。

据了解,这主要与单片集成涉及在单个半导体衬底上创建整个集成电路,所有组件均在单一制程中制造在一起有着莫大的关系。受惠于这样的设计,由于组件非常接近,单片设计通常可以提供*的性能;与此同时,这种接近性还减少了信号延迟和功耗,使单片芯片成为高性能计算的理想选择;此外,单片集成可以缩芯粒尺寸并降低功耗;再者,单片设计中的片上通信速度更快,因为组件在物理上更接近,从而实现更低的延迟和更好的整体系统性能。

因此,这种紧凑的设计可以累计数十亿或数万亿次计算。而按照台积电的说法,我们很快就会有更复杂的单片芯片,拥有超过 1000 亿个晶体管。但构建如此大型的处理器变得越来越复杂和昂贵。同时,随着芯片尺寸变得更大,晶圆良率问题变得更加突出。

有见及此,许多公司选择了chiplet设计(如AMD 的 Instinct MI300X 和英特尔的 Ponte Vecchio 由数十个芯粒组成),这与这种设计拥有很多优势有关。首先,芯粒可轻松实现集成电路的可扩展性和定制化。制造商可以混合和匹配芯粒来创建具有不同功能的产品,使它们能够适应不同的应用;其次,芯粒的模块化特性允许并行开发,从而缩短新产品的上市时间。公司可以同时开发各个芯粒,从而加快创新速度;再者,制造较小的芯粒比生产大型单片设计更具成本效益,特别是对于良率可能较低的先进节点;最后,较小的芯片具有较高的良率,因为单个有缺陷的芯粒不会导致整个产品无法使用;此外,芯粒还可以通过针对所需任务进行优化的处理元件来 提供增强的性能。

在芯粒设计大行其道的同时,也对封装提出了更多的需求,因为只有更好的封装和互联,才能将这些芯粒更好地集成到一起,这正是台积电及其客户必须同步开发逻辑技术和封装技术的原因。前者为后者提供密度改进,这也正是台积电将生产节点的演变和封装技术都包含在同一张幻灯片上的原因。

先进封装,新战场

早前,半导体行业观察曾经报道过,美国将投资30亿美元发展先进封装,这足以证明了之前不被看好的封装的重要性。基于此,芯片制造商也可以以更有效的方式将不同类型的组件封装在一起,而不是使用*进的工艺制造芯片的每个部分。这样可以提高性能,同时降低成本。

以台积电为例,他们在封装技术上就已经投入巨资。今年七月,台积电就表示,由于先进封装产能供不应求,公司计划斥资近新台币900亿元,于竹科辖下铜锣科学园区设立生产先进封装的晶圆厂。

台积电同时还表示,公司的目标是在 2024 年将其称为 CoWoS 的先进封装产能翻一番,该技术代表公司基板上的晶圆上的芯片,具体而言就是将逻辑和存储芯片捆绑在一起,并提高了它们之间的数据传输速度。除此以外,台积电还有被称为多项封装技术,这就是公司现在被称为3D Fabric的平台。在半导体行业观察之前的文章中,我们能看到这家晶圆厂巨头在封装上面的具体表现。

除了台积电以外,晶圆代工竞争对手英特尔和三星也在先进封装上“斗法”。

首先看英特尔,作为一家把持芯片制造技术多年的半导体巨头,英特尔在单芯片集成上有着丰富的经验。来到封装领域也不例外。值得一提的是,在去年的IEDM上,英特尔就率先提出了2030 年打造包含 1 万亿个晶体管的处理器的雄心。

按照英特尔所说,之所以能够实现如此创举,是因为公司的组件研究小组的研究人员已经发现了模糊封装和硅之间界限的新材料和工艺。英特尔同时还揭示了将摩尔定律扩展到封装上万亿晶体管的关键后续步骤,当中包括可以实现额外 10 倍互连密度的先进封装,从而实现准单片芯片。英特尔还指出,公司材料创新还确定了实用的设计选择,可以使用仅 3 个原子厚的新型材料满足晶体管微缩的要求,使该公司能够继续超越 RibbonFET 的规模。

至于三星,同样也在封装上年有了很多投入。

据三星介绍,公司除了拥有2.5D 封装技术I-Cube 和 H-Cube外,还拥有3D IC技术X-Cube。其中,I-Cube部署并行水平芯片放置以提高性能,同时防止热量积聚。三星的硅通孔 和后段生产线 (BEOL) 技术为两个或多个芯片协调其专业功能奠定了基础,超越了各个部分的总和,为现代设备提供了强大的解决方案。根据插入器类型,I-Cube 可用于 I-CubeS 和 I-CubeE 衍生产品。

3D IC 封装则通过垂直堆叠组件,使用更短的互连线长度,从而进一步提高性能,从而实现超高垂直互连密度和更低的寄生效应,同时节省大量片上空间。三星表示3D IC X-Cube技术通过 3D 集成显著降低了大型单片芯片的良率风险,能够以更低的成本实现高系统性能,同时保持高带宽和低功耗。

除了这些厂商以外,日月光、安靠和长电也是先进封装市场不能忽略的重要玩家。

万亿晶体管,台积电的办法

从上面的报道可以看到,先进封装是台积电走向万亿晶体管的必然倚仗。从上图可以开到,除此以外,台积电还将依赖新的沟道材料、EUV、Metal Oxide ESL、Self-Aligned Line w/Flexible Space和Low Damage/Hardening Low-kamp; Novel Cu Fill等多种技术以实现万亿的目标。

下面,让我们来拆解一下台积电的这些“谜底”。

首先看沟通材料方面,据台积电所说,在 7nm 节点之前的所有 CMOS 技术中,硅一直是*的晶体管沟道材料。但到了5纳米技术时代,台积电首此采用SiGe作为p型FinFET沟道材料的先进逻辑生产技术。现在,台积电的晶体管研究团队也在探索基于具有本质上 2D 或 1D 载流子传输的材料构建的器件。包括过渡金属二硫属化物、石墨烯纳米带和碳纳米管等材料正在台积电内部进行研究和测试。

在近两年的IEDM上,我们看台积电的研究人员展示了只有一个原子厚的 MoS2。该团队将原子层沉积形成的铪基电介质与单层 TMD 材料 MoS2 集成,构建了物理电介质厚度为 3.4 nm、电等效氧化物厚度 约为 1 nm 的顶栅 nFET。

至于EUV,则可能是设计High NA EUV或者面向未来的Hyper NA EUV,在这里我们就不在讨论,详情可参考半导体行业观察之前的文章。

台积电在路线图中还提到了Metal Oxide ESL、Self-Aligned Line w/Flexible Space和Low Damage/Hardening Low-kamp; Novel Cu Fill。关于上述技术,我们有了基本的了解,但未从相关检索中看到有关资料。

但可以肯定的是,万亿晶体管芯片正在前面等着我们,这一切都值得我们期待。

参考链接

声明:免责声明:此文内容为本网站转载企业宣传资讯,仅代表作者个人观点,与本网无关。仅供读者参考,并请自行核实相关内容。